**Prerequisites**

Students should feel comfortable using computers. A rudimentary knowledge of programming language concepts and electrical fundamentals (8.02) is assumed. Each student must have an Athena account to access the software used to complete the lab assignments.

Lectures

TR 1 - 2 in 32-123

## Recitation Sections

| #  | Time  | Room   | Instructor |

|----|-------|--------|------------|

| 1  | WF 10 | 26-322 | Brad       |

| 2  | WF 11 | 26-322 | Brad       |

| 3  | WF 11 | 34-303 | Silvina    |

| 4  | WF 12 | 34-303 | Silvina    |

| 5  | WF 12 | 34-304 | Li-Shiuan  |

| 6  | WF 1  | 34-304 | Li-Shiuan  |

| 7  | WF 1  | 34-303 | Chris      |

| 8  | WF 2  | 34-303 | Chris      |

| 9  | WF 2  | 36-155 | David      |

| 10 | WF 3  | 36-155 | David      |

|    |       |        |            |

(Final assignments will be made after the first lecture)

Section assignments are made by the registrar; please plan to attend your assigned section.

If extraordinary circumstances make it impossible to attend the section you have been assigned, you may request a section reassignment by emailing 6004-headta@csail.mit.edu a request to be reassigned to a new recitation time.

### Staff

| Duties                                | Name                      | Email<br>(@mit.edu)   | Office     | Phone   |

|---------------------------------------|---------------------------|-----------------------|------------|---------|

| Lectures                              | Steve Ward                | ward                  | 32-G786    | x3-6036 |

| Head TA                               | Eben Kunz                 | ekunz@mit.edu         |            | -       |

| Admin<br>Asst                         | Cree Bruins               | cbruins@csail.mit.edu | 32-G784A   | x3-2629 |

| + + + + + + + + + + + + + + + + + + + | Chris Terman              | cjt                   | 32-G790    | x3-6038 |

| R R                                   | Li-Shiuan Peh             | peh                   | za dala zd |         |

| Recitations                           | Silvina Hanono<br>Wachman | silvina               | - 1010     |         |

| yk yyla                               | David Crowell             | dcrowell              |            |         |

| 1116.2                                | Brad Gaffney              | bgaffney              |            |         |

| LAs | Becky Bianco | renminbi | <br> |

|-----|--------------|----------|------|

|     | Daniel Gray  | haiiro   | <br> |

The Head TA is in charge of most 6.004 operational issues, including section assignments. You can email the 6.004 Head TA at 6004-headta@csail.mit.edu.

**Text**

There is no required text for the course this semester. Readings for some of the course material will be available on-line.

Handouts

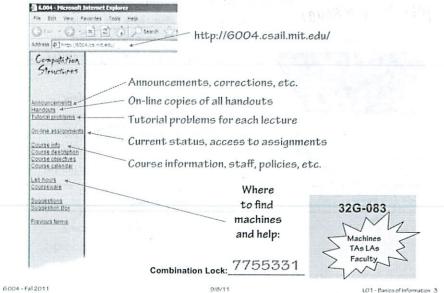

On-line versions of the handouts (in PDF format) can be found at this website.

Problem sets

There are no weekly graded problem sets. Instead there are on-line tutorial problems with answers you can use to test your understanding of the material. The WF recitations give you a chance to work on these problems with the help of the course staff and to ask any questions that you may have.

**Collaboration** The assignments are intended to help you understand the material and should be done individually. You are welcome to get help from others but the work you hand in must be your own. Copying another person's work or allowing your work to be copied by others is a serious academic offense and will be treated as such. We do spot-check submissions to the on-line checkoff system for infractions of the collaboration policy. So please don't tempt fate by submitting someone else's work as your own; it will save us all a lot of grief.

Labs

There are eight lab assignments due at various times during the term and an optional design project at the end of the term. Completing each part of a lab earns points that count toward your final grade. Points are determined during a short interview about each with a member of the course staff. Note that you can submit your work for a lab more than once, for example, as you complete each part. After completing the work on some of the labs, you'll be presented with some on-line lab questions to answer (these are different than the tutorial questions mentioned above). And you'll need to schedule a short lab checkoff meeting for each lab with a member of the course staff. This meeting can happen after the lab's due date but to receive full credit it must be completed within one week of the due date.

You must have a non-zero score for each required lab and all on-line lab questions must be checked-off as a prerequisite for passing the course. A missing required lab (i.e., a lab with a score of 0) will result in a failing grade; incompletes will not be given for unfinished laboratory work.

The lab gets crowded just before an assignment is due so plan accordingly. The lab will be staffed by the course staff during the late afternoon and evening M through R, and during the afternoon on F.

The 6.004 lab is located in 32-083 and is open 24 hours a day, 7 days a week. An access code is required for entry; it will be given out during lecture. The lab offers Linux-Athena workstations that can be used to complete the homework assignments. It is also possible to complete the assignments using

your own computer: the lab software is written in Java and runs in Sun's Java 2 Standard Edition (J2SE) environment (see <u>Courseware</u> for details). The lab serves as a meeting room for 6.004 students and staff; staff members keep their office hours in the lab, whose schedule is posted elsewhere on the 6.004 web site.

Late policy for labs: The on-line system will give you 50% of any points earned for submissions after the due date. So if your first submittal is late, you get 50% of the points. But if you submitted on-time for 15 points, and then late for 25 points, you'll get 20 points total for the lab. Note that points reported by JSim/BSim at check-in are for on-time submittals; you can check your on-line status page to see how many points count toward your total. This will be reported as "0" until you complete your checkoff meeting.

Late policy for checkoffs: The on-line system will allow only 50% of any points earned by your lab (including any late penalties you incurred) if you don't complete your checkoff before the checkoff deadline. So if you miss both the lab deadline and the checkoff deadline, you'll only get 25% of the total points.

Quizzes

There are 4 fifty-minute, closed-book quizzes. The questions will be similar (perhaps identical!) to the <u>tutorial problems</u> and will ask you to provide short, written answers and/or explanations. The quizzes are scheduled roughly every three weeks during recitation:

| Quiz   | Date given | Deadline for grade corrections |

|--------|------------|--------------------------------|

| Quiz 1 | Fri, 9/23  | Wed, 10/5                      |

| Quiz 2 | Fri, 10/14 | Wed, 10/26                     |

| Quiz 3 | Fri, 11/4  | Wed, 11/16                     |

| Quiz 4 | Fri, 12/2  | Wed, 12/14                     |

To ensure everyone has a seat, please attend your assigned section on quiz days. If <u>exceptional</u> circumstances make it impossible to take a quiz at your assigned time, please contact your recitation instructor *before* the quiz to see if other arrangements can be made. Requests for make-ups after the quiz has been given are unlikely to be successful.

There is no final exam.

Grading

The final grade is determined by performance on the quizzes (30 points/quiz, 120 points total), the labs and the design project (90 points total). In addition, you must have a non-zero score for each of the required labs and all the on-line lab questions must be checked off as a prerequisite for passing the course. A missing required lab will result in a failing grade; incompletes will

not be given for unfinished laboratory work.

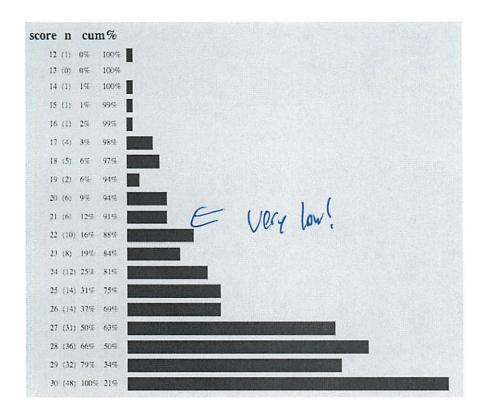

Once your combined score has been computed as explained above, here's how grades will be assigned:

| Grade                                  | Requirement              |

|----------------------------------------|--------------------------|

| A                                      | 175 ≤ total points       |

| В                                      | 155 ≤ total points < 175 |

| С                                      | 135 ≤ total points < 155 |

| D                                      | 115 ≤ total points < 135 |

| F total points < 115, missing required |                          |

## 6.004 at a glance: Fall 2011

| Tue                                                                                  | Wed                       | Thu                                                                                     | Fri                      |  |

|--------------------------------------------------------------------------------------|---------------------------|-----------------------------------------------------------------------------------------|--------------------------|--|

| Registration Day                                                                     | NO CLASS                  | L1 Sep 08 Course overiew & mechanics. Basics of information.                            | R1 Sep 09                |  |

| L2 Sep 13 Digital abstraction, combinational logic, voltage-based encoding.          | R2 Sep 14                 | L3 Sep 15 CMOS technology; gate design; timing                                          | R3 Sep 16                |  |

| L4 Sep 20<br>Canonical forms; synthesis, simplification                              | Holiday                   | L5 Sequential logic. Lab 1 (CMOS) due                                                   | R4 Sep 23<br>QUIZ 1      |  |

| Sep 27 Storage elements, finite state machines.                                      | R5 Sep 28                 | L7 Scp 29 Synchronization, metastability. Lab 2 (Adder) due                             | <b>R6</b> Sep 30         |  |

| L8 Oct 04 Pipelining; throughput and latency.                                        | R7 Oct 05                 | Case study: multipliers. Lab 3 (ALU) due                                                | R8 Oct 07                |  |

| Columbus Day                                                                         | R9 Oct 12                 | L10 Oct 13  Models of computation, programmable architectures.                          | R10 Oct 14  QUIZ 2       |  |

| L11 Oct 18 Beta instruction set architecture, compilation.                           | R11 Oct 19                | L12 Oct 20 Machine language programming issues. Lab 4 (TM) due                          | R12 Oct 21               |  |

| L13 Oct 25 Stacks and procedures.                                                    | R13 Oct 26                | L14 Oct 27  Beta implementation.  Lab 5 (Assy Lang) due                                 | R14 Oct 28               |  |

| Multilevel memories; locality, performance, caches                                   | R15 Nov 02                | L16 Nov 03  Cache design issues                                                         | R16 Nov 04 QUIZ 3        |  |

| L17 Nov 08 Virtual memory: mapping, protection, contexts                             | R17 Nov 09                | L18 Nov 10 Virtual machines: timesharing, OS kernels, supervisor calls Lab 6 (Beta) due | Veteran's Day            |  |

| L19 Nov 15 Devices and interrupt handlers, preemptive interrupts, real-time issues   | R18 Nov 16                | L20 Nov 17 Communication issues: busses, networks, protocols Lab 7 (Trap Handler) due   | R19 Nov 18               |  |

| L21 Nov 22 Communicating processes: semaphores, synchronization, atomicity, deadlock | R20 Nov 23                | Thanksgiving                                                                            |                          |  |

| L22 Nov 29 Pipelined Beta implementation, bypassing                                  | R21 Nov 30                | L23 Dec 01 Pipeline issues: delay slots, annulment, exceptions Lab 8 (Tiny OS) due      | R22 Dec 02               |  |

| Parallel processing, shared memory, cache coherence, consistency criteria            | R23 Dec 07                | L25 Dec 08 Wrapup Lecture!                                                              | R24 Dec 09 <b>QUIZ 4</b> |  |

| No lecture                                                                           | No recitation PROJECT due | Finals - 6.004 is over!                                                                 |                          |  |

generated by glancegen.py 8/30/2011 SAW

9/8

## Welcome to 6.004!

Handouts: Lecture Slides, Calendar

6.004 - Fall 2011

9/8/11

modified 9/5/11 12:01

LO1 - Basics of Information 1

## Course Mechanics

## Unlike other big courses, you'll have

NO evening quizzes

NO final exam

NO weekly graded problem sets

## Instead, you'll face

Repository of tutorial problems (with answers)

FIVE quizzes, based on these problems (in Friday sections)

Lextra ciedit

EIGHT labs + on-line lab questions + Design Contest (all labs and olqs must be completed to pass!)

${\sf ALGORITHMIC}\ assignment\ of\ your\ grade!$

6.004 - Fall 2011

9/8/11

LO1 - Basics of Information 2

## 6.004: Course Clickables

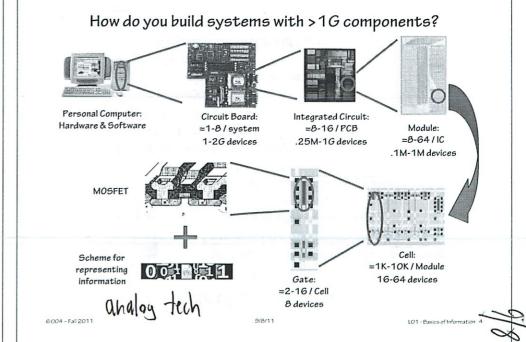

## What do we see?

- Structure

- hierarchical design:

- limited complexity at each level

- reusable building blocks

- · Interfaces

- Key elements of system engineering; typically outlive the technologies they interface

- Isolate technologies, allow evolution

- Major abstraction mechanism

What makes a good system design?

- "Bang for the buck": minimal mechanism, maximal function

- reliable in a wide range of environments

- accommodates future technical improvements

I see a bug in

6.004 - Fall 2011

LO1 - Basics of Information 5

Whirlwind, MIT Lincoln Labs

## Our plan of attack...

- Understand how things work, bottom-up

- \* Encapsulate our understanding using appropriate abstractions

- Study organizational principles: abstractions, interfaces, APIs.

- \* Roll up our sleeves and design at each level of hierarchy

- Learn engineering tricks

- history

- systematic approaches

- algorithms

- diagnose, fix, and avoid bugs

6.004 - Fall 2011

LO1 - Basics of Information 6

First up: INFORMATION

If we want to design devices to manipulate, communicate and store information then we need to quantify information so we can get a handle on the engineering issues. Goal:

good implementations

- ·Easy-to-use

- ·Efficient

- ·Reliable

- ·Secure

٠...

- ·Low-level physical representations

- · High-level symbols and sequences of symbols

had teu+

oce

memor

LO1 - Basics of Information 7

What is "Information"?

Claude Shannan Formalized defin

information, n. Knowledge communicated or received concerning a particular fact or circumstance.

Pats WON their 18th game

Tell me something new.

"Really, NO FINAL!"

Information resolves uncertainty. Information is simply that which

cannot be predicted.

The less predictable a message is, the more information it conveys!

LO1 - Basics of Information &

6004 - Fall 2011

## Quantifying Information

(Claude Shannon, 1948)

Suppose you're faced with N equally probable choices, and I give you a fact that narrows it down to M choices. Then I've given you

Information is measured in bits (binary digits) = number of O/1's required to encode choice(s)

log<sub>2</sub>(N/M) <u>bits</u> of information

Examples:

- information in one coin flip:  $log_2(2/1) = 1$  bit

- roll of 2 dice: log2(36/1) = 5.2 bits

- outcome of a Red Sox game: 1 bit (well, actually, are both outcomes equally probable?)

(Thy-still ned to know who actually won)

5.004 - Fall 2011

Loh vailable/huffman tree

Need milliple games for Fixed-length encodings

If all choices are equally likely (or we have no reason to expect otherwise), then a fixed-length code is often used. Such a code will use at least enough bits to represent the information content.

ex. Decimal digits  $10 = \{0,1,2,3,4,5,6,7,8,9\}$ 4-bit BCD (binary coded decimal)

$\log_2(10) = 3.322 < 4bits$

ex. ~86 English characters =

$\{\text{A-Z}\,(26),\,\text{a-z}\,(26),\,\text{O-9}\,(10),\,\,\text{punctuation}\,(11),\,\text{math}\,(9),\,\text{financial}\,(4)\}$

7-bit ASCII (American Standard Code for Information Interchange)

$\log_2(86) = 6.426 < 7bits$

6.004 - Fall 2011

9/8/11

LO1 - Basics of Information 11

## Encoding

- Encoding describes the process of assigning representations to information

- Choosing an appropriate and efficient encoding is a real engineering challenge

- Impacts design at many levels

- Mechanism (devices, # of components used)

- Efficiency (bits used)

- Reliability (noise)

- Security (encryption)

Next lecture: encoding a bit. What about longer messages?

04-Fall 2011 Loday

LO1 - Basics of Information 10

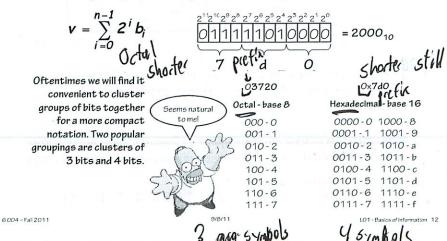

## Encoding numbers

It is straightforward to encode positive integers as a sequence of bits. Each bit is assigned a weight. Ordered from right to left, these weights are increasing powers of 2. The value of an n-bit number encoded in this fashion is given by the following formula:

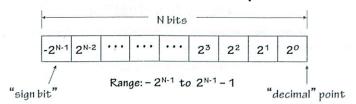

# Haw to represent (-) # Signed integers: 2's complement

8-bit 2's complement example:

$$11010110 = -2^7 + 2^6 + 2^4 + 2^2 + 2^1 = -128 + 64 + 16 + 4 + 2 = -42$$

If we use a two's complement representation for signed integers, the same binary addition mod 2" procedure will work for adding positive and negative numbers (don't need separate subtraction rules). The same procedure will also handle unsigned numbers!

By moving the implicit location of "decimal" point, we can represent fractions too:

$1101.0110 = -2^3 + 2^2 + 2^0 + 2^{-2} + 2^{-3} = -8 + 4 + 1 + 0.25 + 0.125 = -2.625$

6.004 - Fall 2011

9/8/11

LO1 - Basics of Information 13

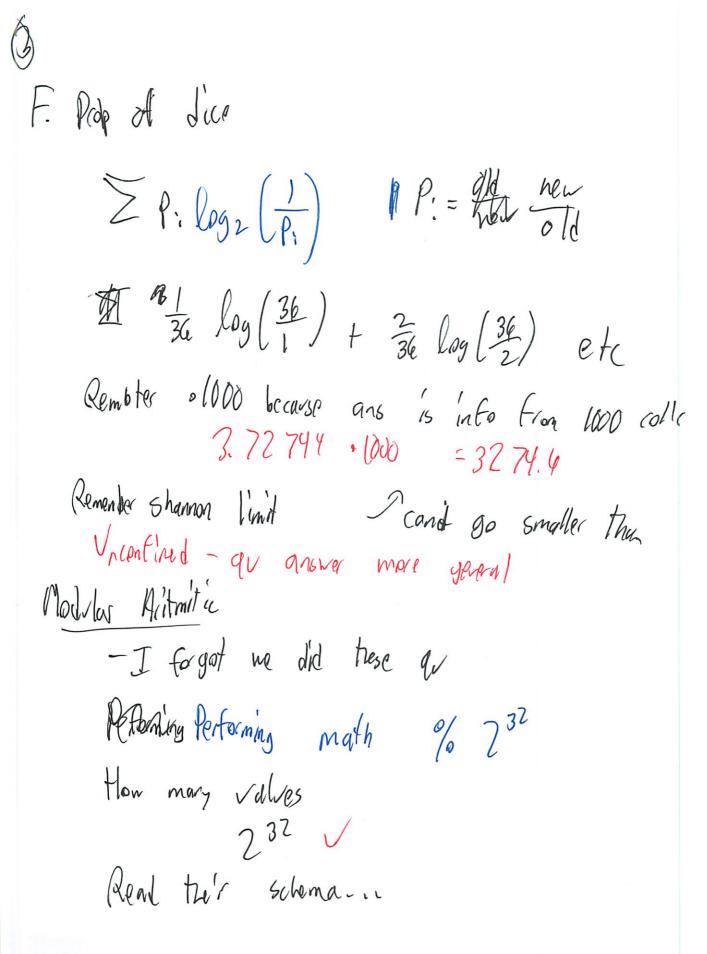

## When choices aren't equally probable

When the choices have different probabilities ( $p_i$ ), you get more information when learning of a unlikely choice than when learning of a likely choice

Information from choice<sub>i</sub> =  $log_2(1/p_i)$  bits Average information from a choice =  $\sum p_i log_2(1/p_i)$  best (ase

#### Example

| choice; | Pi   | log2(1/p) |

|---------|------|-----------|

| "A"     | 1/3  | 1.58 bits |

| "B"     | 1/2  | 1 bit     |

| "c"     | 1/12 | 3.58 bits |

| "D"     | 1/12 | 3.58 bits |

Average information

- = (.333)(1.58) + (.5)(1)

- + (2)(.083)(3.58)

- = 1.626 bits

Can we find an encoding where transmitting 1000 choices is close to 1626 bits on the average? Using two bits for each choice = 2000 bits

6.004 - Fall 2011

9/8/11

LO1 - Basics of Information 14

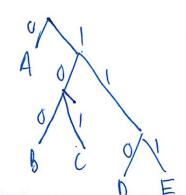

## Variable-length encodings

(David Huffman, MIT 1951)

Use shorter bit sequences for high probability choices, longer sequences for less probable choices

| choice; | Pi   | encoding |

|---------|------|----------|

| "A"     | 1/3  | 11       |

| "B"     | 1/2  | 0        |

| "c"     | 1/12 | 100      |

| "D"     | 1/12 | 101      |

| В  | С   | Α        | В   | A  | D  |

|----|-----|----------|-----|----|----|

| 0. | 100 | 11       | 01  | 1- | 10 |

|    | 0   | ٨        | 1   |    |    |

|    |     |          | X   |    |    |

|    | В   | 9        | / \ | 1  |    |

|    | 0/  | $\wedge$ | 1   | A  |    |

|    | Ċ   |          | ľ   | ,  | •  |

|    |     |          |     |    |    |

Average information = (.333)(2)+(.5)(1)+(2)(.083)(3)= 1.666 bits

Transmitting 1000 choices takes an average of 1666 bits... better but not optimal

Huffman Decoding Tree

To get a more efficient encoding (closer to information content) we need to encode sequences of choices, not just each choice individually. This is the approach taken by most file compression algorithms...

Over the block

- like ZIP

LOT-Basics of Information 15

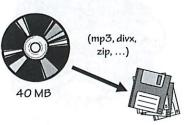

## Data Compression

Key: re-encoding to remove redundant information: match data rate to actual information content.

"Outside of a dog, a book is man's best friend. Inside of a dog, its too dark to read..."

-Groucho Marx

Ideal: No redundant info - Only

4 MB

unpredictable bits transmitted. Result appears *random!*

LOSSLESS: can 'uncompress', get back original.

A84b!\*m9@+M(p

6.004 - Fall 2011

9/8/1

LO1 - Basics of Information 16

## "Able was I ere I saw Elba." \*1024

Compressed: 138 bytes

6.004 - Fall 2011

9/8/11

## Is redundancy always bad?

Simplifes tech Encoding schemes that attempt to match the information content of a data stream are minimizing redundancy. They are data compression techniques.

"around on which the human hand of man has never before set foot"

However, sometimes the goal of encoding information is to increase redundancy, rather than remove it. Why?

- · Make the information easy to manipulate (fixed-sized encodings)

- · Make the data stream resilient to noise (error detecting and correcting codes)

Does recompression work?

If ZIP compression of a 40MB Bible yields a 4MB ZIP file, what happens if we compress that?

6.004 - Fall 2011

·Do we get a 400 KB file?

· Can we compress that, to get a 40K file??

· Can we compress the whole Bible down to a single bit???

· IsitaOora 1????

redundancy!

perfectly, the result has no

Calmagolive Complexity

Size of smallest Program

to generate tree

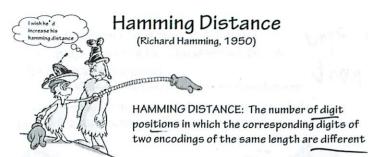

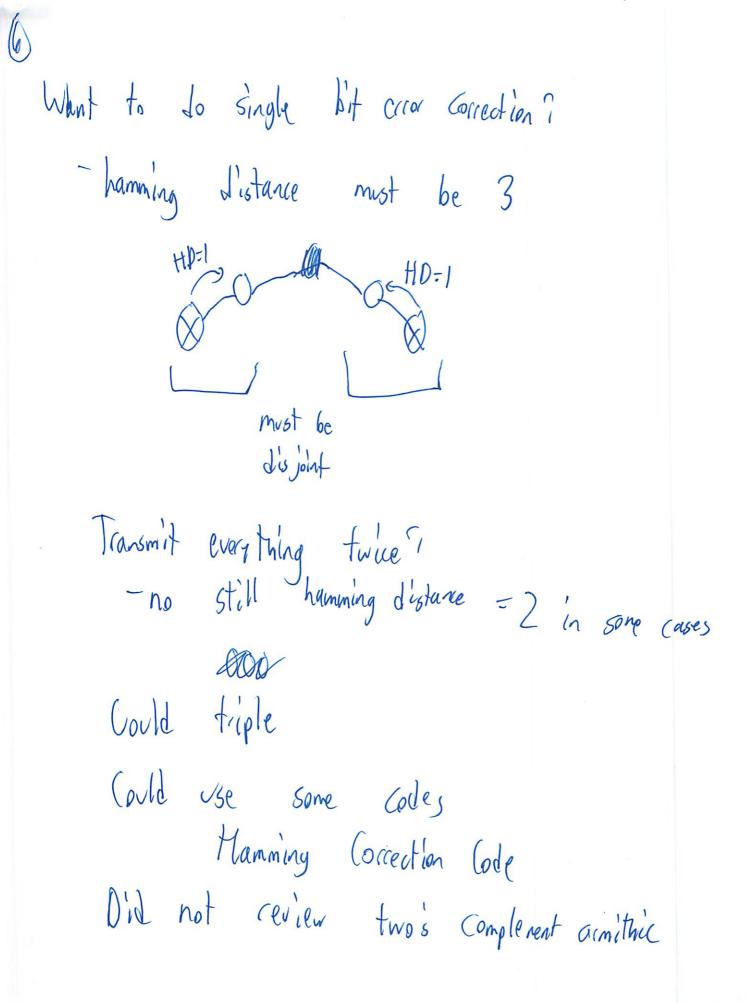

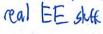

## Error detection and correction

Suppose we wanted to reliably transmit the result of a single coin flip:

Heads: "O"

Tails: "1"

This is a prototype of the "bit" coin for

Further suppose that during transmission a single-bit error occurs, i.e., a single "O" is turned into a "1" or a "1" is turned into a "O".

LO1 - Basics of Information 20

6.004 - Fall 2011

101 - Basics of Information 19

The Hamming distance between a valid binary code word and the same code word with single-bit error is 1.

The problem with our simple encoding is that the two valid code words ("O" and "1") also have a Hamming distance of 1. So a single-bit error changes a valid code word into another valid code word...

6.004 - Fall 2011

LO1 - Basics of Information 21

- bit errors

# Increase hamming Error Correction J'estance to 101 "tails" J'e (10) 100 110 "tails" If D is the minimum Hammir distance between code words, we can correct up to

By increasing the Hamming distance between valid code words to 3, we quarantee that the sets of words produced by single-bit errors don't overlap. So if we detect an error, we can perform error correction since we can tell what the valid code was before the error happened.

- Can we safely detect double-bit errors while correcting 1-bit errors?

- · Do we always need to triple the number of bits?

LO1 - Basics of Information 23

### Error Detection

What we need is an encoding where a single-bit error doesn't produce another valid code word.

If D is the minimum Hamming distance between code words, we can detect up to (D-1)-bit errors

We can add single-bit error detection to any length code word by adding a parity bit chosen to quarantee the Hamming distance between any two valid code words is at least 2. In the diagram above, we're using "even parity" where the added bit is chosen to make the total number of 1's in the code word even.

Can we correct detected errors? Not yet...

6.004 - Fall 2011

101 - Basics of Information 22

## The right choice of codes can solve hard problems

Reed-Solomon (1960)

First construct a polynomial from the data symbols to be transmitted and then send an over-sampled plot of the polynomial instead of the original symbols themselves spread the information out so it can be recovered from a subset of the transmitted symbols.

Particularly good at correcting bursts of erasures (symbols known to be incorrect)

Used by CD, DVD, DAT, satellite broadcasts, etc.

Viterbi (1967)

A dynamic programming algorithm for finding the most likely sequence of hidden states that result in a sequence of observed events, especially in the context of hidden Markov models.

Good choice when soft-decision information is available from the demodulator.

Used by QAM modulation schemes (eg, CDMA, GSM, cable modems), disk drive electronics (PRML)

6.004 - Fall 2011

9/8/11

LO1 - Basics of Information 24

6004 - Fall 2011

## Summary

- · Information resolves uncertainty

- · Choices equally probable:

- · N choices down to M⇒ log<sub>2</sub>(N/M) bits of information

- · use fixed-length encodings

- · encoding numbers: 2's complement signed integers

- · Choices not equally probable:

- · choice, with probability  $p_i \Rightarrow \log_2(1/p_i)$  bits of information

- · average number of bits =  $\sum p_i \log_2(1/p_i)$

- · use variable-length encodings

- · To detect D-bit errors: Hamming distance > D

- · To correct D-bit errors: Hamming distance > 2D

#### Next time:

- · encoding information electrically

- · the digital abstraction

- · combinational devices

6.004 - Fall 2011

9/8/11

LO1 - Basics of Information 25

Chris Terman lots of options 4 fidays - quittes on friday

the much into ? Measure Roya (8)

reasure rean nation to an nfolentropy

in bits log ( Prob) infolentropy k bits > 2k different choices 4.1 bits & 5 bits if one bon it have multiple, can use variable-length encoding

X = 8 bits

2° Choices for value

= 256

Y 10 1 1 1 1 1 1

Hamming distance = 1

50 now narrow to 8 choices

The into is lope  $\log_2\left(\frac{1}{256}\right)$

= log 2 (25)

= 5 6ils

abstract measure

Sometimes had to cationalize

6.004 is his far class

Mulfman Code

Want to encode Bad Dad Voing 1st tree 100 0 110 110 0 0 110 B A D D A DO Now deading 0 100 0 111 A B A E Short sequence = high probability Like P(A) = 5 P(B) = p(C) = P(D) = P(E) = 125

A M. 15 E 14 D .15 Brill Fæe

| 9 |                    |             |    |

|---|--------------------|-------------|----|

|   | Build From bottom  | Up          |    |

|   | AI                 | Mex         |    |

|   | Then remains table |             |    |

|   | AII                | 3           |    |

|   | E, (               | 1           |    |

|   |                    | 2           |    |

|   |                    | 15<br>15    |    |

|   | Êtc                | 1.          | ٠  |

|   |                    | AI.3<br>E.4 |    |

|   |                    | 00.3        |    |

|   | Etc                | AIOU        | 6  |

|   | AI OU              | E           | .6 |

|   | Finish             | Tiee        | l  |

|   | E T O U            | TIEE        | ·  |

|   | ,, 100             |             |    |

Optimal log2 (15) = 2.74 So our code for I letter is worse than dig (an Code words to get better What is any length of 600 char nessage 14.6.3 =  $\frac{40 + 180}{2 \cdot 12} = 2 \cdot 2 \cdot \frac{bits/char}{char}$ 7 Oh no / 100 since length of whole nessage 220 bits

Fixed Length Code

36it

A 000

E 010

100

100

**Preface**

6.004 Compatational Structures

This text approaches the field of digital systems architecture with a particular bias, one kindled during years of observation of M.T.T. students and speculation about the factors that distinguish outstanding engineers from the merely very competent majority. We bring to the project a conviction that the distinction reflects attitudes and perspectives that are at most subtle by-products of the usual technical education: subliminal lessons occasionally administered to students by virtue of accidental discovery rather than deliberate pedagogy. The organization and approach of *Computation Structures* is geared to the explicit cultivation of these characteristics in every student and reader.

#### Scope and Mission

As computer systems become increasingly complex, their study inevitably relies upon more specific areas of specialization. We compartmentalize specific technologies—logic elements, processors, compilers, operating systems—as subdisciplines to be treated by separate courses, texts, and intellectual tools. Interfaces between the subdisciplines are powerful engineering abstractions that allow, for example, the designer of a processor to deal entirely in the domain of digital logic, naively exploiting the electronic circuitry in the abstraction below and providing interpretive services to software in the abstraction above.

The abstractions work sufficiently well that our curricula (and, for that matter, our job descriptions) accommodate specialists whose understanding of computer systems is cripplingly incomplete. We confer computer science degrees on theorists who may be helpless when programming is required, on hardware designers to whom the high-level structure of the system to which they contribute is mystery, and on programmers who lack a clear understanding of how or why their programs make real things happen. Often what passes for technical breadth takes the form of multiple specialties: Students exhibit pockets of local facility, unable to connect them into an effective understanding of the system as a whole. Such people can and do perform useful functions, but their potential for creativity is limited by their acceptance of the boundaries of their specialties. They shy from the challenge to venture beyond familiar approaches, to reshape problems, to develop new interfaces and revise existing ones; they accept the mysterious rather than unveiling it, oversensitized to their own limitations. They are, in effect, imprisoned by the abstractions they have been taught.

Outstanding students, in contrast, somehow develop a perspective that illuminates the interfaces between technologies, rather than the technologies themselves, as the

9/10

most important structural elements of their discipline. They view the interfaces with respect but not reverence; they examine both sides of an abstraction, treating it as an object of study rather than a boundary between the known and the intractably mystical. They have discovered the power of their own universality; typically they have built complete systems, often with meager resources, and made them work. They have the sophistication, and most importantly the self-assurance, to explore new abstractions and to appreciate the role and costs of existing ones.

Computation Structures is intended to produce renaissance engineers of this latter category. To this end, it deliberately telescopes much of computer science into a bottom-up progression that builds simple electronics into representative computer systems. The student is catapulted through one layer after another of implementation technology, an experience that accentuates technological interfaces and the structure induced by them. The breadth of coverage of the book reflects our compulsion to demystify its subject matter. We are unwilling to ask students to accept a technology on faith, or to postpone its penetration to some more advanced course. The spectrum of implementation technology is laid before them as a challenge to sample, to uncover, to discover their capacity to master its entirety.

The ultimate mission of *Computation Structures* is not so much to convey facts as to catalyze personal discoveries by each student: the ability to master a wide range of technical details, the self-assurance to dive through a technological boundary, the power to grab a wire-wrap gun or CAD tool or body of code and create new structures. The considerable volume of technical detail is present largely to serve this goal; it is not the subject of the book, but rather a tool by which we convey its more important lesson.

#### The Text

Computation Structures does not presume to replace the many excellent texts that focus on established subtopics such as logic design or operating systems; nor is it intended for an elite audience capable of digesting four semesters of course work in a single term. It covers topics that every engineer—certainly every computer scientist—should be aware of, in sufficient detail to establish a concrete connection between each topic and practical reality. In many cases that connection is provided by the MAYBE computer, a simple microarchitecture that we use as a running example throughout the text. The MAYBE is presented in sufficient detail to allow its actual construction and operation, an activity required of M.I.T. students; even in the absence of such experience, it provides a subject for close scrutiny and a context for concrete discussions and questions.

The text is introductory, presuming no formal background in digital systems; however, it generally assumes a level of technical sophistication consistent with that of an undergraduate engineering student. The text makes repeated connections to related technical areas. These should enrich the presentation for students with appropriate backgrounds, but are inessential to the sequel; for example, early chapters include a few circuit diagrams whose appreciation requires an Ohm's-law level of circuit sophistication. Programming ideas and constructs are introduced with a lack of fanfare that presumes some previous exposure to computers and programming on the part of the student. A subset of the C language, used for sample programs, is

presented in a terse appendix; we have found that students easily attain a level of C fluency that allows them to read and understand the examples.

The text does not make extensive use of real-world case studies, relying instead on the more coherent framework designed into our real but parochial example machines. Connections to the technical literature and to industrial practice are identified primarily in sections entitled Context; these provide pointers for deeper investigation of technical issues, links to adjacent fields, and occasional historical perspective.

#### Role at M.I.T.

Computation Structures is used at M.I.T. as the text for 6.004, a one-term, Shour-perweek sophomore "core" course required of all electrical engineering and computer science undergraduates. Three of the fifteen student hours are allocated to laboratory activities; the remainder are spent in classes and homework. Typical students have previously taken 6.001, a LISP-based programming course that uses Abelson and Sussman [1985] as a text, and 6.002, an introductory circuits course. The role of 6.002 is primarily to prepare the student for the 6.004 laboratory component, in which (for example) familiarity with an oscilloscope is assumed. 6.001 provides a first exposure to many ideas that recur in 6.004—programs, stacks, memory locations—albeit in a quite different context and often following a different idiom.

6.004 is a fast-moving course, stretching to accommodate the subject in its tightly packed single-term syllabus. Major topics are dealt with in about 25 lectures, which generally follow the order of the text and average one or two lectures per chapter. Substantial pruning is required to provide coherent if somewhat superficial coverage in lectures: While the major topics of the text are each dealt with in some depth, many of their ramifications and issues raised in the text are not addressed explicitly. Many of the optional (starred) sections are omitted, although the mix varies somewhat from one term to the next.

The big picture emerging from the lectures is embellished by smaller section meetings held twice weekly, by homework, and by laboratory assignments. These components provide a vehicle for sampling underlying technical detail, stimulating each student to relate the lecture topic with at least one example of practical reality. The cultivation of this connection is a key element of the course and this text. Rather than presenting a stack frame in abstract terms, for example, we encourage each student to come to grips with the entire set of nested implementation technologies that make it real—machine language, microcode, circuit diagrams, logic gates. Frequent probes to concrete reality reinforce the two major lessons of the course: first, the value of abstractions as a tool for structuring complex systems; and second, the capacity of the individual student to master *any* aspect of a system he or she cares to focus on.

#### Laboratory Work

These key lessons of *Computation Structures* are reinforced by the laboratory component of the course. Each student is required to construct, debug, and program a working MAYBE computer from simple components (at the level of ROMs and registers). Several machine architectures—stack and general-register machines—are implemented and programmed using a common microarchitecture.

oh ... 9

Preface

xvii

Students' computers are constructed from reusable take-home kits. The kits have a selection of logic components as well as integral prototyping board, power supply, and very primitive input/output provisions. Workstations (with a variety of support programs) and oscilloscopes are available in the laboratory. Although the wiring and much of the debugging can be performed by students at home, final checkout and subsequent program development require the use of facilities in the lab.

The laboratory is structured as about eight assignments, each directed at a fairly tightly constrained set of goals. The directedness of the assignments differentiates the activity from more advanced "project" laboratories, which emphasize initiative and creativity; however, each assignment contains some nugget of creative challenge, such as the design of a machine instruction. A major creative outlet takes the form of an optional design contest, held at the end of each term, in which students are given a relatively free hand to modify their machines to improve performance on a benchmark program that is not revealed until the day of the contest. Each entrant is constrained to use only parts from the lab kit, although we allow n-student teams to combine n lab kits, normalizing the performance of such entries by a factor of n. (The best performance by this metric has come from two-kit entries.)

In order to make the student computer construction tractable and reasonably failsafe, we have developed a set of printed-circuit modules (compatible with protoboard construction techniques) and a staged approach to construction whose early phases involve the use of a kernel subset of the machine to debug its incremental improvements. This methodology, involving the use of bootstrapping and scaffolding to develop complex systems, is among the major lessons of the course; it is one we have found no way to teach without hands-on experience.

The integration of a "complete" laboratory with a broad-spectrum architecture course makes an ambitious package, but one that produces students whose technical maturity and self-assurance is based on that ultimate educator: They have each built a computer and made it work. We enthusiastically recommend the approach.

While we value the *omniware* breadth of the laboratory, much of its pedagogy can be captured by somewhat less extreme programs. The majority of the laboratory activity involves coding at some level, and can be carried out effectively using simulation software rather than hardware implementations. Several simulators and related system software (available both for UNIX workstations and for PCs) provide a convenient development test bed for microcode and software, even where the alternative of a hardware MAYBE machine exists. Since the architectural personality of our machine is largely dictated by the contents of a control ROM, the range of architectural options that can be explored using reprogramming and simulation techniques is relatively unconstrained. An effective laboratory can thus be fashioned using only commonly available computing resources.

In the absence of such resources, the complete implementations presented here can still be explored in a kind of ersatz laboratory whose medium is paper rather than machinery, that is, in assignments that probe, modify, and analyze the given structures. This approach was used at M.I.T. in years prior to the 6.004 laboratory; while the latter has clear advantages, a paper laboratory devoted to all levels of a single coherent example accomplishes many of the demystification and perspective-

building goals of our current course.

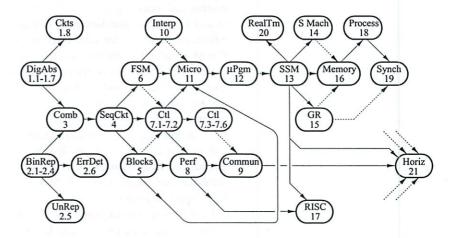

#### Alternative Paths through the Text

The subject of the text lends itself well to subsetting by suppression of detail, and we expect individual courses and readers to deemphasize or omit selected subtopics to suit their needs and backgrounds. The (widely varying) dependencies among topics are mapped crudely by the following graph:

Relatively inessential dependencies are shown as dotted edges. The level of detail shown in the diagram ignores certain subtleties, often bundling essential and optional issues together as single nodes. Some additional guidance to topic selection is provided by observing sections marked with an asterisk, indicating digressions that can be skipped without compromising subsequent (nonasterisked) coverage.

Topic selection and path through the text may be adjusted to accommodate a number of different course needs. A two-term undergraduate sequence based on the text would allow careful and relaxed treatment of its entire coverage and, given  $\Lambda$   $\Lambda$ sufficient student time, is an attractive alternative to the single-term firehose-style course offered at M.I.T. An introductory graduate course might augment the text by selected readings from the literature; candidates appear in the Context sections and in the bibliography. Certain of the exercises appearing at the end of each chapter are marked with one or two asterisks to indicate that they may be challenging for an introductory undergraduate course. A single asterisk suggests that the marked problem requires more than routine application of the principles of the chapter; double asterisks identify problems that should challenge graduate students.

#### Acknowledgments

Computation Structures reflects the ideas, influence, and efforts of literally dozens of people who have contributed to 6.004 and its ancestors over the years. This lineage begins with the seminal course 6.032, which was developed in the late 1960s by Jack Dennis and subsequently evolved under the auspices of Jon Allen and Bob Gallager. The book owes its name and much of its sense of direction to these early roots; it

Preface

conveys, to a considerable extent, lessons that have been taught its authors by their predecessors.

The current course began to take shape during the spring of 1980, when the authors collaborated with Dave Reed in an effort to modernize 6.032 and its course notes. Subsequent years saw a succession of significant revisions to the course, each accompanied by a rewrite of the notes, exploring a variety of pedagogic formulae. The birth of the MAYBE in 1984 marks the point at which the book's current content and focus began to jell; the efforts of Dan Nussbaum and Chris Terman played a significant role during this formative period. Subsequent maturation of the laboratory work included substantial contributions to the MAYBE by Ziggy Blair, Ken Mackenzie, Joe Morgan, and Henry Houh.

During this long history, the course and its notes were scrutinized by dozens of course staff and thousands of students, whose contributions to the surviving text are real but generally so diffused as to be unidentifiable. Exceptions, whose impact is more conspicuous, include Tom Anderson, Andy Ayers, Dave Goddeau, Mark Johnson, Rob Kassel, Ken Mackenzie, Rishiyur Nikhil, Dan Nussbaum, Jon Powell, Gill Pratt, Jerry Saltzer, Chris Terman, and John Wolfe. Valuable discussions, critique, and feedback on the text have been provided by Anant Agarwal, Bill Dally, Jacob Katzenelson, Jim Kirtley, Al Mok, Bruce Musicus, Steve Seda, Gerry Sussman, Rich Zippel, and many others.

Particular credit is due John Wolfe for the massive effort he devoted to conversion of the source manuscript to TeX, to Eva Tervo and Sharon Thomas for the help they lent and the aggravation they sustained in preparing the manuscript, to Larry Cohen for his skilled and tireless editing, and to the Harris Corporation, whose HCX-9 was used to format the book with blazing speed. And to Don Knuth, that premier computer scientist whose contributions have been varied, prolific, and influential, we are indebted for TeX, which deserves simultaneous recognition as the text formatter of choice and the most idiosyncratic programming language known to us. It is impossible to account for the prenatal debt incurred by the book to the authors' wives, Debbie and Louise, whose loving encouragement nursed it through its long gestation.

The authors are grateful to M.I.T. for providing an environment that led to *Computation Structures*, to the Department of Electrical Engineering and Computer Science for support of the course development surrounding the text, and to Hewlett-Packard and Tektronix for their donations to the 6.004 laboratory. Finally, a decade of 6.004 and 6.032 students deserve sympathy and thanks for their role as subjects of a long succession of educational experiments as well as credit for the result. They, after all, are more than an influence; they are the reason.

The key to the orderly design of complex systems, digital or otherwise, lies in the decomposition of their function into modules whose behavior can be independently and concisely specified. To encourage this functional modularity and simplify the specifications for each module, we adopt a variety of engineering disciplines and agree to abide by the constraints they impose; in programming, for example, conventions for the representation of data and for passing parameters are typical self-imposed constraints. Each such discipline involves a set of primitive elements, each performing some prescribed basic function, together with rules for the construction of new elements by the composition of existing ones. The power of an engineering discipline derives from its simplification of the functional specifications of each module by the abstraction of essential function from nonessential detail; the description of a square-root procedure, for example, must confront the arithmetic relationship between its input and output but need not deal with the patterns of bits used to represent them.

We can observe two broad classes of activities in the structuring of complex systems. The first and more common of these involves working within a single discipline, enriching its repertoire by combining existing functions to define new ones. The appropriate software analogy is the construction, within the framework of a particular programming language, of a library of procedures to perform various useful functions. The second and more radical structuring activity involves the use of the modules of one discipline to define and support a new, higher-level abstraction with its own primitive elements and composition rules. In software design, such radical structuring typically involves the use of a lower-level language (together with its library of support procedures) to implement a higher-level language whose primitives and composition rules are in some (perhaps application-dependent) sense more powerful. The major characteristic of the new level is that it isolates its user from the underlying implementation technology, as opposed to simply adding new options to it.

Typically the structure of complex systems shows an alternation between these two activities. Functional extensions are made to some discipline until its complexity becomes unwieldy, at which point it is used to support a new abstraction with a manageable number of higher-level primitives and composition rules.

Such abstractions and the disciplines that support them are the central theme of computer science. Every significant digital system involves many levels of discipline, each implementing a more powerful set of primitive elements and composition rules

than the ones that underlie it. This chapter presents the fundamental abstraction that bridges the gap between the domain of the circuit designer (whose primitive elements are electronic components) and that of the computer architect.

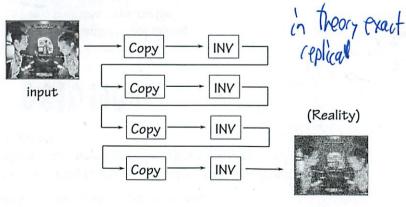

#### 1.1 Information and the Digital Abstraction

The primary use of electronic devices is the processing of information. Major appliances such as televisions and computers serve to translate information from one format to another—from an encoded radio frequency input to an output picture, or from a string of input symbols to a corresponding string of output symbols. Each such complex information processor is synthesized from components that transform, combine, store, and manipulate representations of information. Thus we can dissect a television and identify the information-processing functions of its major subsystems, specifying the way in which the input and output information of each is encoded into electronic signals. We might further scrutinize each subsystem, documenting the function performed by each component in information-handling terms, down to the level of fundamental circuit elements.

A capacitor, for example, is an energy storage device; in typical applications, its stored energy may be viewed as the electronic representation of stored information (such as elapsed time, in an RC timer circuit). While the electronic representations of information in a television typically involve continuous variables (such as voltages or frequencies), the symbolic information processed by a computer consists of discrete units such as binary digits.

Digital systems, in general, are based on technology for the electronic representation of discrete information units; they offer the important advantage that the information content of each electronic signal is easy to quantify. They illustrate a powerful and important engineering principle: the pursuit of simplicity through constraint. Digital engineering involves a self-imposed design discipline that allows systems to be analyzed in the simple, abstract domain of logic rather than the vastly more complicated domain of underlying electronic principles. The advantages and mechanism of this abstraction are explored briefly in the following paragraphs.

The amount of information carried in a discrete-valued signal s may be defined as  $\log_2 N_{\rm v}$ , where  $N_{\rm v}$  is the number of distinct values of s that can be reliably set and measured. It is conventional to take the logarithm in base 2 and express the result in bits, or binary digits, of information. We might propose, for example, to communicate each decimal digit d by means of a d-volt signal on a particular wire, so that  $N_{\rm v}$  is 10. If our measurement technology is accurate enough to distinguish reliably between the ten values, the information conveyed by each signal is  $\log_2 10 = 3.322$  bits. If our measurement tells us only whether or not the signal is below 5 V, however,  $N_{\rm v}$  is 2 and the amount of information conveyed is  $\log_2 2$  or 1 bit.

A single bit is the minimum amount of information necessary to distinguish reliably between two values; it is the smallest convenient quantum for discrete information

log 2 to get bits

<sup>&</sup>lt;sup>1</sup> There are situations in which this view is inappropriate, such as applications in which a capacitor is used as a storage medium for energy to power other devices.

dh ...

representations and serves as the basic unit of information storage and communication in most digital systems. It is noteworthy that 1 bit is exactly the information content of a single digit in a binary number system, which makes binary (rather than, say, decimal) an attractive and popular choice for the representation of numbers in digital systems.

Electronic parameters such as voltages are, to a good first approximation, continuous variables; we quantify them by real numbers rather than by integers. Each such parameter can in theory assume infinitely many distinct values, even over a bounded range; a voltage between 0 and 1 V may be 0.23 V or 0.6713 V or 0.6713456278 V. If we were able to set and measure such a voltage exactly, it would carry an infinite amount of information (since  $N_v$  would be infinite). Of course, noise and other physical realities limit our ability to constrain and measure physical parameters. A measurement of 0.23 V indicates that 0.23 V is a more likely value than, say, 0.3 V, which in turn is more likely than 0.4 V. The actual amount of information conveyed by our measurement is awkward to quantify exactly; it depends on the accuracy and reliability characteristics of the measuring device as well as electrical noise and other detriments to the validity of the signal itself. A typical signal level might carry 10 or 12 bits of useful information, on the average, with moderate reliability. Such representations are ideally suited to applications (such as television) involving large volumes of information flow and in which occasional errors are not catastrophic. The synthesis and analysis techniques used in these situations typically assume that each signal represents the corresponding real number to an acceptable accuracy, thus avoiding the need for precise quantification of its information content.

### 1.2 Representation of Discrete Variables

In many applications, it is convenient to use components whose behavior can be simply and precisely characterized in informational terms. A printer device connected to a computer can take as input the representation of a character to be printed, from an alphabet of, say, 128 possible characters. We would like the communication from the computer to the printer to be highly reliable: The printer must be able to determine precisely the character to be printed from the signals it receives. The amount of information conveyed to the printer is thus  $\log_2 128 = 7$  bits for each character printed. The communication technique used will of course involve wires carrying continuously variable signals (such as voltages), but to reach our reliability goals we may be willing to sacrifice much of the information-carrying potential of each signal. A typical parallel printer interface, for example, involves seven independent wires, each carrying 1 bit of information encoded as a voltage. Each wire selects one of two alternative values (say, a 1 or 0 as the value of a corresponding binary digit), and the seven-wire aggregate thus identifies one of  $2^7 = 128$  possible characters.

The reliable translation between a discrete variable such as a binary digit and its representation as the approximate value of a continuous variable such as a voltage provides the key to what we call the *digital abstraction*. It allows us to use conventional circuit elements to build a family of *digital devices* whose information-processing characteristics can be specified as a simple logical function involving discrete inputs

Oh that is what that mean!

The Digital Abstraction

as long as reliable -don't care about it

ASCIT

3

#### 1.3 Combinational Devices

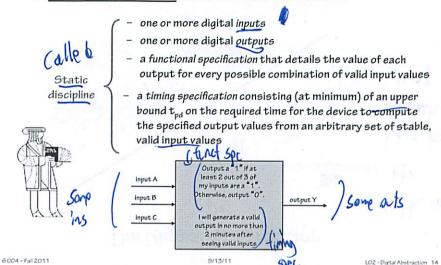

The simplest and most fundamental abstraction in the repertoire of the digital engineer is the *combinational device*, which we formalize as follows:

A combinational device is a circuit element having the following properties:

- one or more discrete-valued input terminals;

- · one or more discrete-valued output terminals;

- a functional specification, detailing the value of each output for each of the possible combinations of input values; and

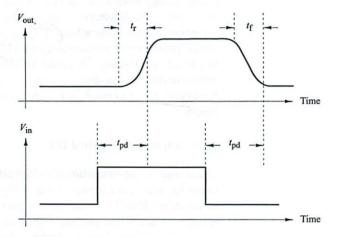

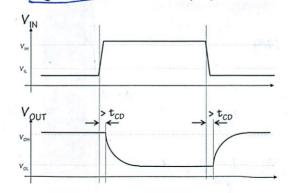

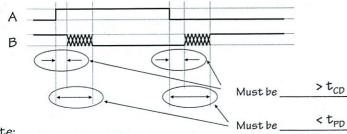

- a timing specification, consisting (at minimum) of an upper bound  $t_{\rm pd}$  on the time required for the device to compute the specified output values from an arbitrary set of input values.

The usual interpretation of the *propagation delay*  $t_{\rm pd}$  is that whenever a particular combination of input values is applied to the device and maintained for at least  $t_{\rm pd}$  seconds, a corresponding set of output values will appear. Moreover, these output values will remain at the output terminals (at least) until the inputs change. Thus a set of input values applied for t seconds results in corresponding output values for a period of at least  $t-t_{\rm pd}$  seconds. Note that  $t_{\rm pd}$  is a *maximum* time required for new input values to be reflected at the output terminals; in general, the *minimum* such time is assumed to be zero.<sup>2</sup> One result of the latter assumption is that output values are contaminated immediately by any change at the inputs, regardless of  $t_{\rm pd}$ .

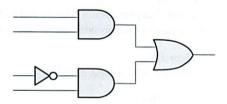

An important feature of combinational devices is the simplicity with which they may be interconnected to synthesize new combinational functions. In particular, new combinational devices may be created by combining combinational elements in acyclic circuits, so long as care is taken not to connect outputs together.

More precisely, we can construct a combinational device by exploiting the basic rule of composition:

**Combinational composition** A circuit is a combinational device if it consists of interconnected circuit elements such that

· each circuit element is itself combinational,

more hardwarey Speck.

2

<sup>&</sup>lt;sup>2</sup> A refinement of this assumption, in which a nonzero contamination delay becomes part of the device specification, is occasionally used in the design of performance-critical circuitry.

- every node of the circuit is either designated as an input to the circuit or connects to exactly one output terminal of a circuit element, and

- the circuit contains no directed cycles (that is, every path through the circuit that traverses elements only in the input-to-output direction visits each circuit node at most once).

(Special memory -diff process

for formula to actually

memorize)

Any of the circuit nodes may be designated as outputs of the new device.

It is easy to verify that this construction yields devices that conform to our combinational criteria. The acyclic constraint allows us to proceed systematically from the circuit's input terminals through successive circuit elements, assigning to each node both a functional specification (as a function of the input values) and a time bound. The functional specification of each noninput node is derived from the specification of the element driving that node together with the functional specification assigned to that element's inputs; similarly, the propagation delay associated with such a node is computed by adding the element's  $t_{\rm pd}$  to the maximum of the delays associated with its input nodes. In general,  $t_{\rm pd}$  for the constructed device becomes the maximum cumulative propagation delay encountered on a path from any input to any output.

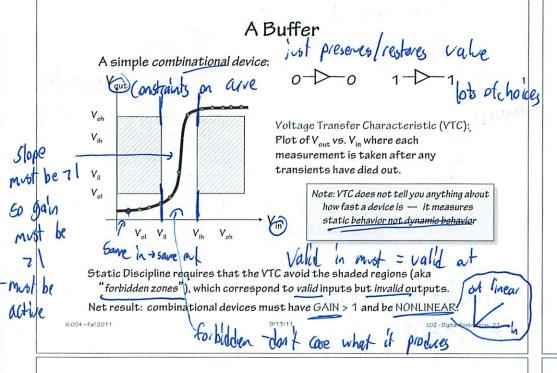

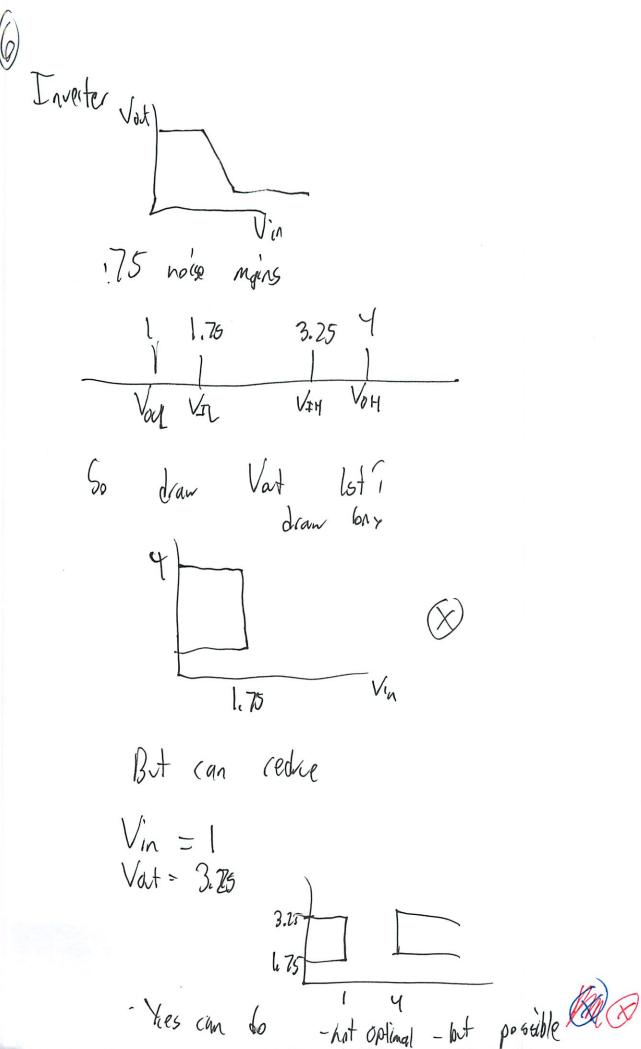

#### 1.4 The Static Discipline: Logic Levels

Kinda &

The fact that we can synthesize arbitrarily complicated combinational devices using acyclic circuits of combinational elements gives us a bootstrapping technique for extending the usefulness of a primitive initial set of such devices; this is vaguely analogous to the induction step of an inductive proof. A remaining task is the development of a basis—an initial set of combinational elements from which we can synthesize more ambitious ones. Clearly we must begin with at least one combinational device that is defined in terms of technologies other than combinational devices. It is in the design of these basic elements that fundamental decisions regarding the representation of the discrete values of our abstraction are confronted.

6.02

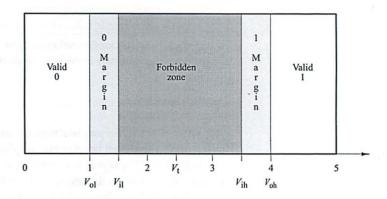

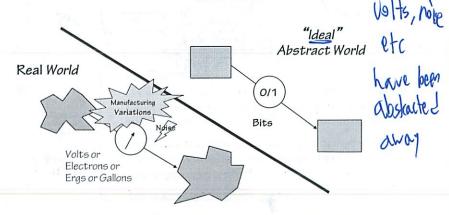

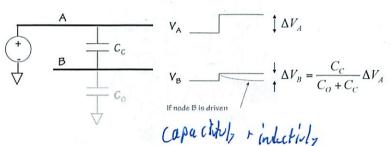

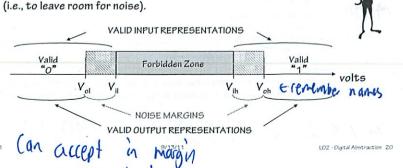

Suppose, for example, that we are to represent a binary (or logical) variable d using a voltage v that can be varied between 0 and 5 V. We might choose to represent d=0 by a voltage of 0 and d=1 by 5 V. The efficacy of this representation then depends on our ability to set and measure v with sufficient reliability that the representation of d=0 is never mistaken for the representation of d=1 and vice versa, a reasonably easy demand to meet. We can afford to be fairly sloppy about setting and measuring v and still deduce the correct value of d. If we guarantee that v will be set to a value below 1 V when d=0 and above 4 V when d=1, and if we ensure that our measurement of v will be accurate to within 0.5 V, we shall always measure a voltage greater than 3.5 V when d=1 and below 1.5 V when d=0. We might distinguish between the two cases by comparing the measured voltage with a 2.5-V threshold voltage  $V_t$  and assuming a logical 1 as the value of d if the measured value is above the threshold and a logical 0 if it is below.

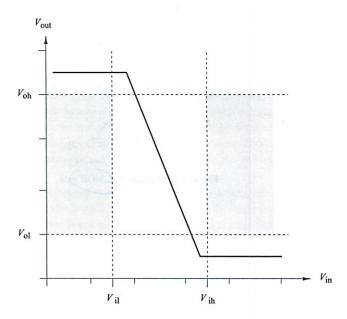

Figure 1.1 shows the mapping of the continuous variable v onto the discrete (binary digit) d. If the measured voltage is near or at the 2.5-V threshold, we will be unable

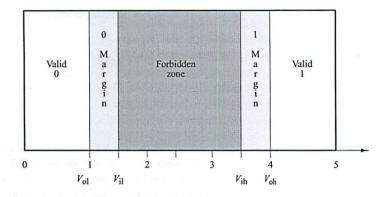

Figure 1.1 Mapping of logic levels to voltage.

to distinguish reliably between the two values of d. We avoid this embarrassing circumstance by outlawing it; we designate the region between 1.5 V and 3.5 V as a forbidden zone that does not correspond to the valid representation of a binary variable. Since we can reliably discriminate between voltages below 1.5 V and those above 3.5 V, adhering to the discipline that v must be set above 4 V or below 1 V ensures that forbidden values are avoided. In fact, we have allowed an extra half-volt margin for error on each side of the forbidden zone; these noise margins allow our scheme to function in the presence of a certain amount of noise or other unanticipated error.

In general, the reliable representation of discrete variables using continuously variable physical quantities requires such ranges of excluded values between valid representations. This gives rise to the possibility of *invalid signals* that correspond to none of the logical values; a wire carrying  $V_{\rm t}$  represents neither a logical 1 nor a logical 0 by the convention outlined above. Such invalid signals are foreign to the digital abstraction and are unaccounted for in the analysis and synthesis methodologies commonly used by the digital engineer.

In order to protect digital designers from unanticipated invalid signals in their circuits, logic elements are commonly designed to conform to a *static discipline*:

how to ensure i

A static discipline is a guarantee that, given logically valid inputs, every circuit element will (after an appropriate propagation delay) deliver logically valid outputs.

The interpretation of "logically valid" is relative to a particular representation convention, which in turn varies with the implementation technology. Typically, however, a single representation convention applies throughout an entire digital system. A static discipline offers a measure of assurance that invalid signals will not arise spontaneously in a well-designed combinational circuit: If the inputs to each device are

well behaved, each device's outputs will also be well behaved after some bounded delay.

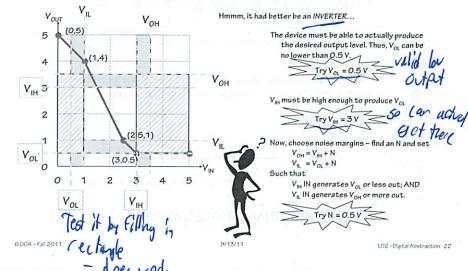

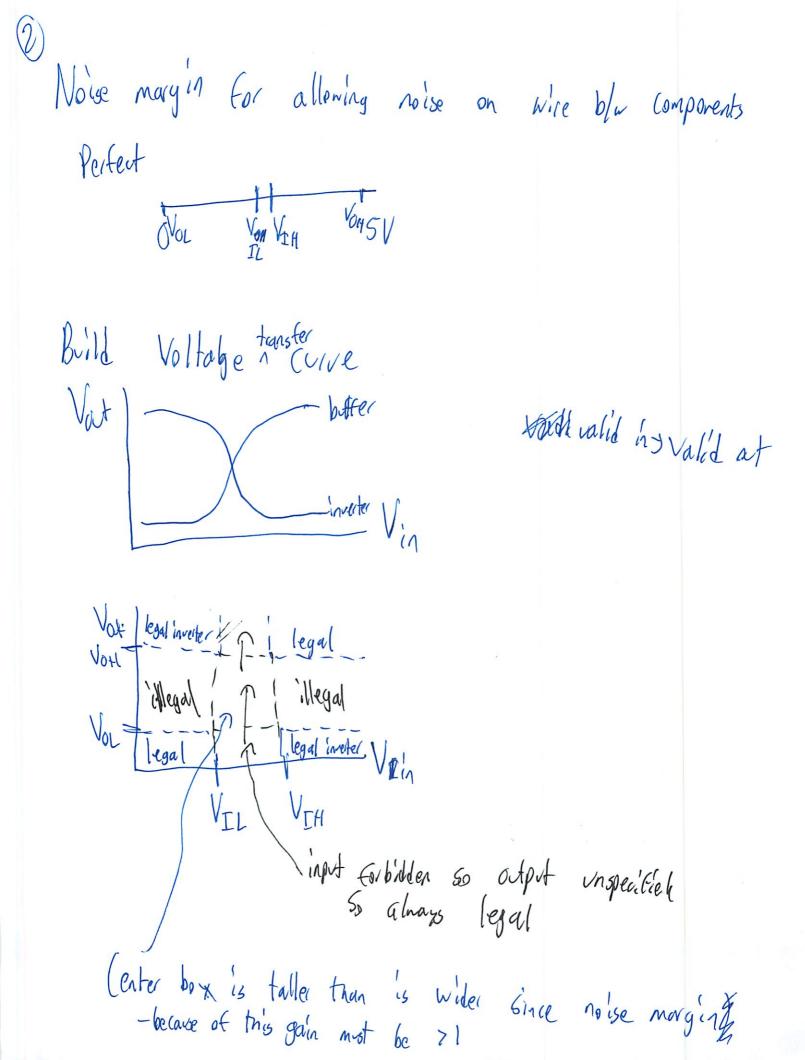

Noise margins amount to imposing a more stringent validity requirement on output signals from a device than apply to its inputs, ensuring that marginally valid input signals are restored to unquestionable signals at the output. The threshold  $V_{\rm il}$  represents the highest input voltage that must be interpreted as a logical 0; it is higher than  $V_{\rm ol}$ , the highest output voltage that can be asserted to indicate a 0. This ensures that every valid output 0 will be interpreted as a 0 at connected inputs, even after some degradation. A similar relationship holds between  $V_{\rm ih}$  (the lowest input representing a valid 1) and  $V_{\rm oh}$  (the lowest output asserted to indicate a 1).

#### 1.5 Rate of Information Flow

The representation scheme we have developed provides for the *static* transmission of a fixed amount of information—a single bit—as an electric signal over a wire. In general, we expect this value to change from time to time; if it *never* changes, as would occur if the value communicated is a constant, the need for the wire should be questioned! Thus, while at any instant a signal might convey only a single bit of information, it typically carries a *sequence* of bits over a period of time. If we make provisions for changing a signal to represent a new bit of information every second on the second, that signal may be viewed as carrying a *flow* of information at the rate of 1 bit/s; it could be used to transmit a 100-bit binary number in 100 s.

Any scheme we choose for communicating discrete variables places practical limits on the frequency with which we can change their values and thereby constrains the rate of information flow. Rates of information flow in digital systems are often specified in *baud*, or value transitions per second, a parameter that is constrained by the communication *bandwidth* of the underlying (analog) communication medium. A fundamental theorem by Nyquist places an upper bound on a communication channel's useful baud rate of twice its bandwidth, even in the absence of noise. In the case of binary representations, where each value is a binary digit, 1 baud is equivalent to 1 bit/s. Thus the theoretical maximum rate of information flow over a 3000-Hz voice-grade line carrying binary values as two different voltage levels is 6000 bits/s. This limit can be exceeded, in theory, by the use of more than two discrete values at a baud rate of less than 3000 changes per second; using four voltages, for example, raises the theoretical limit of our voice-grade line to 12,000 bits/s.

Of course, the effective rate of information flow can always be increased by using multiple signals; a 100-bit number can be transmitted in 1 s serially using a single 100-baud binary signal or in parallel by means of a hundred 1-baud binary signals, each encoding a single digit. Such choices are faced frequently by designers of digital systems, and a judgment typically depends strongly on underlying technological issues. For example, digital communication between geographically distant subsystems, such as terminals of an airline's flight reservation system, might rely on leased telephone lines whose bandwidth characteristics limit transmitted signals to audio frequencies. Reliable digital communication over such a line is limited to a few thousand baud, but increasing the communication rate by using multiple lines

band = transx per sec

is expensive. Since communication cost is likely to be a dominant factor in the design of such systems, it is worthwhile devoting considerable effort to minimizing the required communication rates.

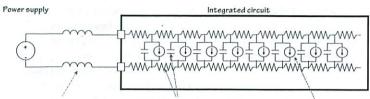

Even in localized systems, communication costs are an important design consideration. As logic elements become cheaper and perform more complex functions, the cost of running wires (or other media) to interconnect them becomes an increasingly important element of system costs. Although nearby modules of a system can communicate at rates measured in hundreds of megabaud by using many parallel wires, such high bandwidth is expensive in device terminals and interconnections and is not to be squandered. Even within a single integrated-circuit chip, where the economies are based largely on space (chip area), interconnection costs often dominate: More of the chip area is devoted to lines transmitting signals from one logic element to another than to the logic elements themselves.

#### 1.6 Transitions and Validity

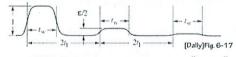

In a dynamic system, where logical variables change in value from time to time, we cannot in practice avoid brief excursions through the forbidden zone. Because of stray capacitance and other such physical constraints, the voltage representing a logical variable v cannot be changed instantaneously from one valid logic representation to the other, although the transition may be quite fast—a few nanoseconds is typical.

We therefore enforce on ourselves an additional discipline: We avoid asking whether v represents a logical 1 or 0 at about the time when it may be making a transition between values. This in turn requires that the beholders of v—those devices to which v is an input—each have available information about when v might change. Most commonly this requirement is met by constructing  $synchronous\ systems$ , in which logic values are constrained to make transitions only at prescribed times (for example, every microsecond on the microsecond) keyed to a globally available clock signal. For truly asynchronous systems, it is impossible to guarantee that no logic level will be sampled at an inauspicious time (for example, during a transition); however, such events can be  $\overline{\text{made quite}}$  improbable in practice. This general topic is visited again in section .

### 1.7 Logic Families

Some of the parameters in figure 1.1 seem arbitrary. The association of low voltage with logical 0 and high voltage with logical 1 is a convention termed positive logic, the dual convention, negative logic, represents logical 0 by the higher of the two voltages. This choice may be made arbitrarily to suit one's taste; a digital system can be analyzed in terms of positive logic, negative logic, or a mixture of the two.

Other parameters, such as the choice of logically valid voltage ranges and threshold voltages, typically reflect a combination of design goals and characteristics of the implementation technology. Several distinct "families" of digital devices have been developed over the years, each with its own set of characteristics and parameters for mapping continuous electronic variables (usually voltage) onto logic (nearly always

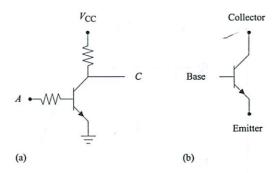

Figure 1.2 Resistor-transistor logic (a) RTL inverter; (b) NPN transistor.

binary) values. Each such family includes a set of rules for the valid representation of logical values; each device in the family has the property that, so long as its inputs obey the rules, its outputs will also. They provide in each case a set of Tinkertoy-like modules that can be simply plugged together to build arbitrarily complex logical systems, with relative disregard for the underlying electronics. The resulting simplicity is an enormous advantage to the designer, who can deal with the concise logical characterization of devices whose specification in electrical terms would be nearly intractable.

# 6.4

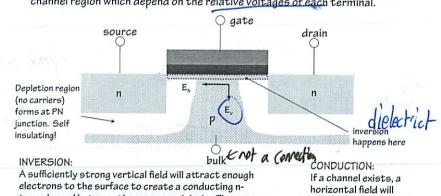

#### 1.8 Digital-Circuit Implementation

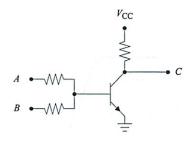

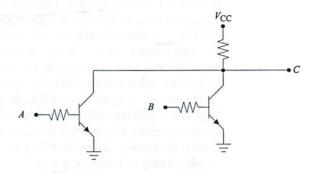

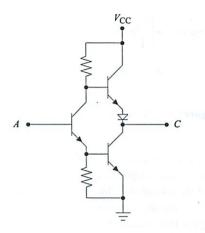

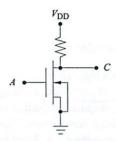

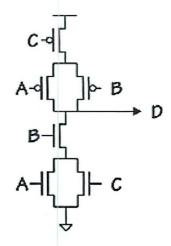

Figure 1.2(a) depicts a simple logic device from an early implementation technology called resistor-transistor logic, or RTL. The device is an inverter; its logical output at C is 1 if its input (at A) is 0, and 0 if its input is 1. The transistor in the circuit of figure 1.2(b) may be viewed roughly as a switch controlled by its base (input) current, which in turn depends on the voltage at A. If the voltage at input A is high (representing, using positive logic, a logical 1 input), then the switch is closed (the collector and emitter are short-circuited) and the output C is effectively connected to ground (yielding a logical 0 output). If the input voltage is close to 0 (logical 0 input), the switch is open, leaving C connected to the supply voltage  $V_{CC}$  through a small resistor; this results in a logical 1 output.

#### 1.8.1 Logic Levels and Noise

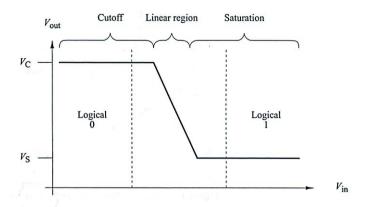

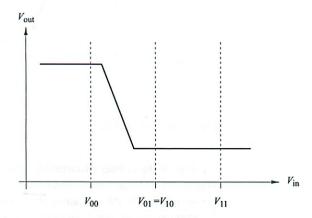

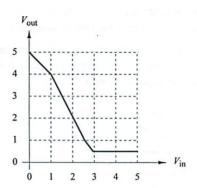

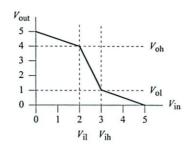

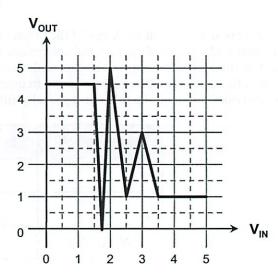

A slightly more sophisticated model of the transistor yields the voltage-transfer characteristics shown in figure 1.3 for our simple inverter.

Over a portion of its input-voltage range, the device behaves like an amplifier with a negative gain (proportional to the slope of the center segment of the plot). This is termed the *active* or *linear* region of operation. When the input voltage is sufficiently low, the transistor is said to be a *cutoff* and effectively presents an open circuit between its emitter and collector. When the input voltage is sufficiently high, the

Wollage

The Digital Abstraction

Figure 1.3 Voltage-transfer characteristics of an RTL inverter.

transistor becomes <u>saturated</u> and effectively short-circuits its emitter to its collector. Details of the sizes of each region of operation (cutoff, active, and saturation) and the exact placement of the "knees" of the transfer characteristic depend on parameters of the transistor (such as its gain) as well as on values of the resistors in the device. The ranges of voltages specified for valid logic levels of 0 and 1, in turn, reflect these details and hence constrain their choice.

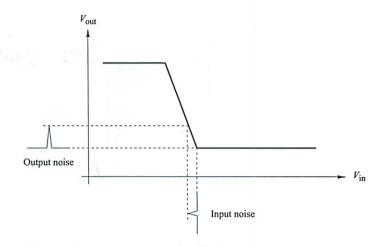

It is important, for example, that the design parameters be such that a valid logic level at the input places the transistor either in the cutoff or saturation region of operation; this avoidance of the active region guarantees reliable performance in the presence of noise. In its active region, the circuit behaves like an amplifier with high gain; if, for example, a valid logical 1 at the input to the device biases the transistor into its linear region, it will amplify small perturbations of the input. Thus a 10-mV noise spike at the input might (assuming a gain of 10) become an 0.1-V noise spike at the output, as sketched in figure 1.4.

The output signal presumably connects to the input of other devices, where its noise component may be amplified further, until the resulting voltages become invalid representations of logic values.

Thus we constrain input voltages representing valid logic values to fall well within the cutoff and saturation regions, where the output voltage will be relatively insensitive to small perturbations of the input. In general, we leave a gap between each range of valid logic levels and the active region of the transistor in order to provide noise margins.

In the RTL logic family, the standard supply voltage  $V_{\rm CC}$  is 3.6 V. Valid logical 0 must be below 1 V, and logical 1 must be above 2.5 V; the resulting noise margins are each about 0.5 V.

#### 1.8.2 Fanout Restrictions

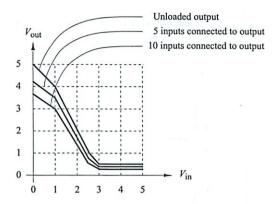

It is necessary to define the valid logic levels so as to include the device's output values when it has logically valid inputs. Having insisted that valid inputs will

Figure 1.4 Amplification of a noise spike.

result in either saturated or cutoff transistor behavior, we find that this reduces to a requirement that the cutoff output voltage  $V_{\rm C}$  and the saturation output voltage  $V_{\rm S}$  be included as valid logical 1 and 0 levels, respectively.

Unfortunately, the characteristic plotted in figure 1.3 oversimplifies the behavior of our device in several ways. One of these is the assumption, made for the purposes of the preceding discussion, that the load on the output of the device imposed by external devices connected to terminal C is negligible. In fact, the voltage drops across the collector resistor and the transistor itself are functions of the output current; the effect of a heavy load on the output of the inverter is, roughly, to move the cutoff voltage  $V_{\rm C}$  and the saturation voltage  $V_{\rm S}$  toward each other and hence toward the forbidden zone between valid logic representations. As a result of this effect, each family of logic implementations imposes a restriction on the number of device inputs to which each device output can be connected; this is called the *fanout* limitation. In the case of RTL, device fanout is only about 5. This is primarily due to the voltage drop across the collector resistor while the transistor is at cutoff (in the logical 1 state), which lowers the output voltage as the fanout (and hence the output current) is increased.

#### 1.8.3 Nonlinearities and Gain

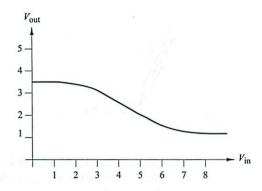

We have seen that the continuous range of voltages between minimum (zero or ground, in our example) and maximum (the supply voltage  $V_{\rm CC}$ ) is divided into several regions: The valid logic levels are at the extremes, a forbidden zone occupies the center portion, and the remaining two gaps constitute the noise margins. It is generally desirable to center the forbidden zone between the valid logic levels, yielding comparable noise margins for logical 0 and 1 values; it is the *minimum* of the noise margins that dictates the maximum tolerable electrical noise level for a logic family.

iden /

Figure 1.5 Ultra-high-gain switching device.

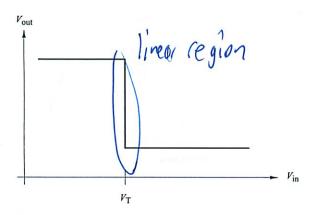

The reader may have noticed that the active region of the transistor, which constitutes its useful range in linear applications (such as in a high-fidelity amplifier) is a positive annoyance in digital applications. The fact that it must be avoided in the assignment of valid logic levels motivates us to minimize its size, thereby allowing more freedom to assign logic levels and noise margins. From this standpoint, an ideal transistor for digital purposes has an infinitesimal linear region, as depicted in figure 1.5.

In this hypothetical device, the linear range is reduced to a vertical line, corresponding to a (negative) infinite gain at a single threshold voltage  $V_{\rm T}$ .